CMOS管(Complementary)

CMOS管的英文全称为Complementary Metal Oxide Semiconductor,全称为互补金属氧化物半导体。也就是说CMOS管,依然是由NMOS和PMOS管构成,其中C指的是一种制造工艺而不是材料特性。

CMOS反相器

CMOS反相器的工作原理

CMOS管的基本想法是通过设置两个开关来控制输出电压的状态。

需要注意的是上述两个开关不能够同时闭合,同时闭合会发生短路。CMOS门电路最根本的一个想法就是:在一个系统中,最好的高电平就是电源,最好的低电平就是地,于是输出时应该尽量向这两者靠近。

CMOS反相器的电路图

对于上面电路而言,分为两部分一部分为NMOS管,一部分为CMOS管。对于接地的MOS管而言,器件类型为NMOS,其源极和衬底与地相连。对于接电源的MOS管而言,其类型为PMOS管,,其源极和衬底与高电平相连。

所以通过分析,我们容易得出,当输入为高电平1的时候,上面PMOS截止,下面NMOS管导通,输出电压为地,同理可知输入为低电平0的时候,接地的NMOS必然截止,上面CMOS必然导通,于是此时输出电压为高电平。

当输入电压在无效区的时候,利用图解法,将上下两条曲线的工作曲线绘制在同一坐标系下,而后得到如下图形:

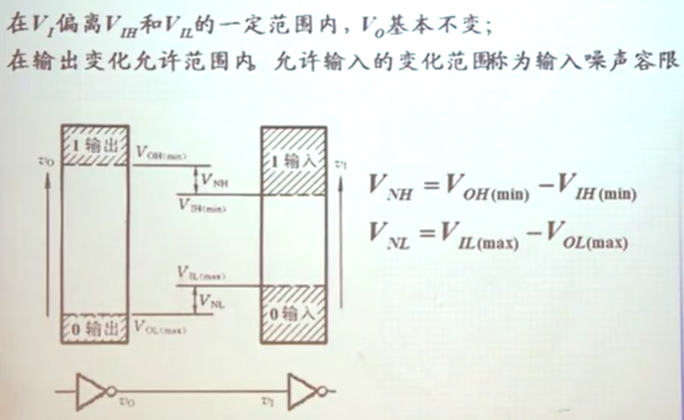

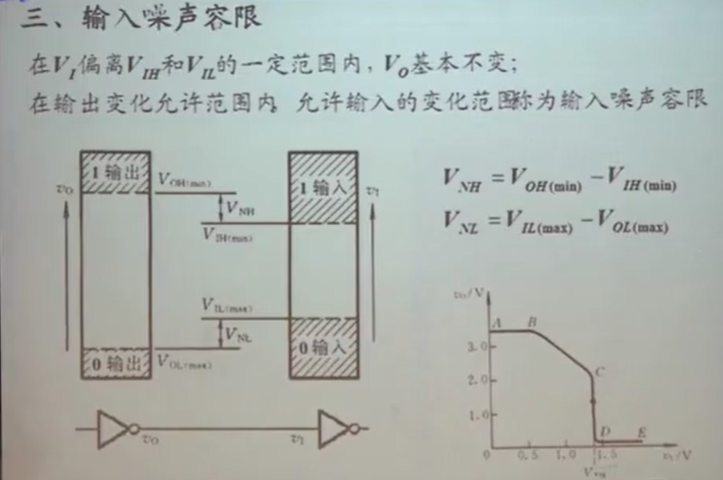

输入噪声容限

在$V_{I}$偏离$V_{IH}$和$V_{IL}$的一定范围内,$V_{0}$基本不变;在输出变化允许的范围内,允许输出的变化范围称为输入噪声容限。

其中:

上述式子也就是表征理想最优输入输出电压(电源、地)和实际输出电压之间最大的噪声误差。

CMOS反向器的输入输出特性

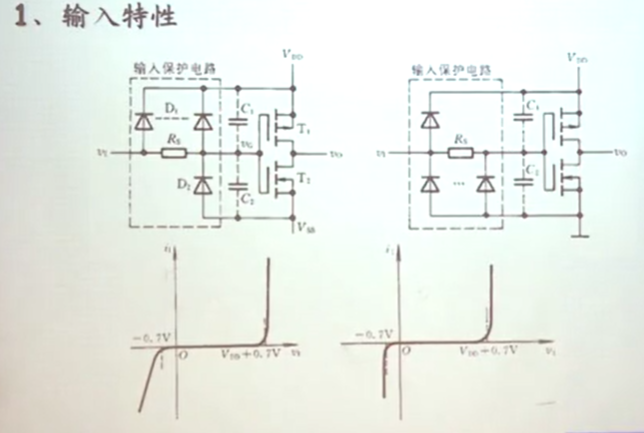

输入特性

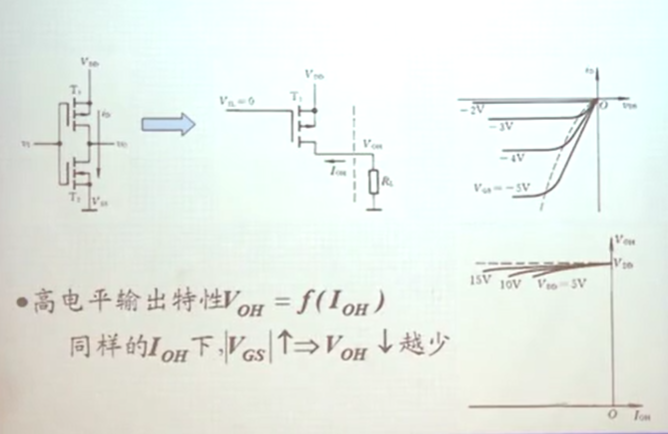

输出特性

输出低电平的时:

输出高电平时:

CMOS反相器的动态特性

传输延迟时间

对于任何电路,都有如下结论:只要是电路必然会在时间上留下哼唧,也就是说,只要是电路就不可避免地在时间上产生延迟。归根结底就是说,任何电路器件从工程实际的角度而言必然存在电容的影响。

对于CMOS反向器而言,其传输延迟时间的主要原因有:

- $C_{I}$和$C_{L}$充放电,因为$R_{ON}$较大,所以$C_{L}$受充放电的影响也比较大

- $t_{PHL},t_{PLH}$受到$C_{L},V_{DD}$影响。

动态功耗

导通功耗

这也就是为什么通过提升VDD,提升噪声容限一般情况下是不可取的。

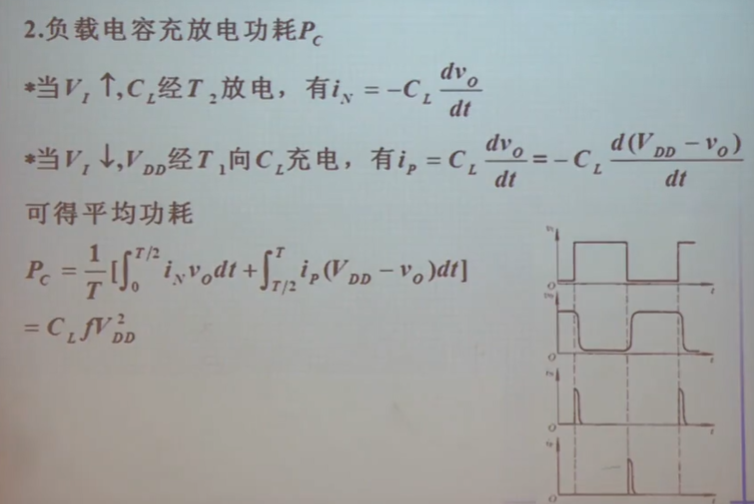

负载功耗

计算过程如下:

总功耗

总功耗 = 动态功耗$P_{D}$+静态功耗$P_{S}$,其中:

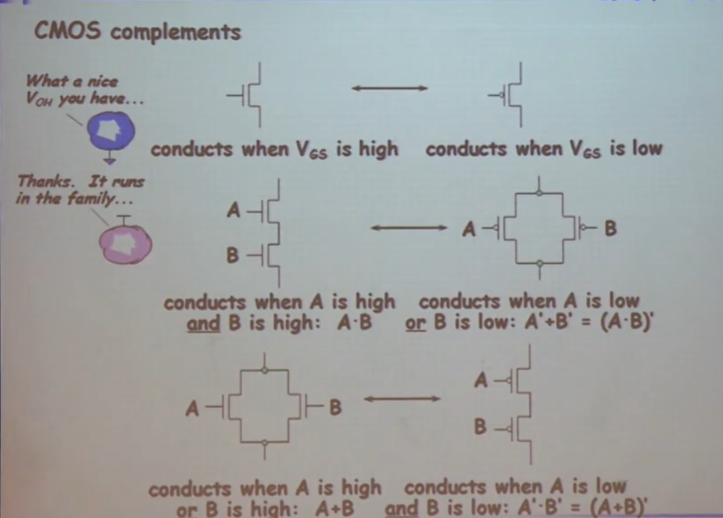

其他CMOS电路

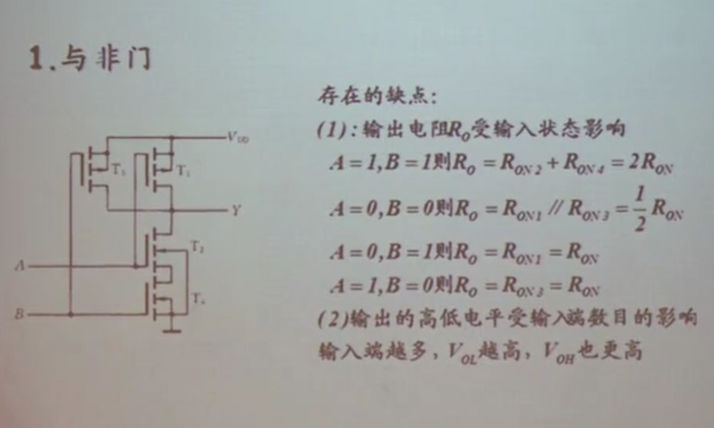

在这种设计中,我们发现对于内阻存在多种情况,一个MOS导通时与多个MOS导通时的内阻情况

不一致,导致此时输出高低电频的质量也不一致,也就是说,对于此时的电路而言,其设计标准并不统一。

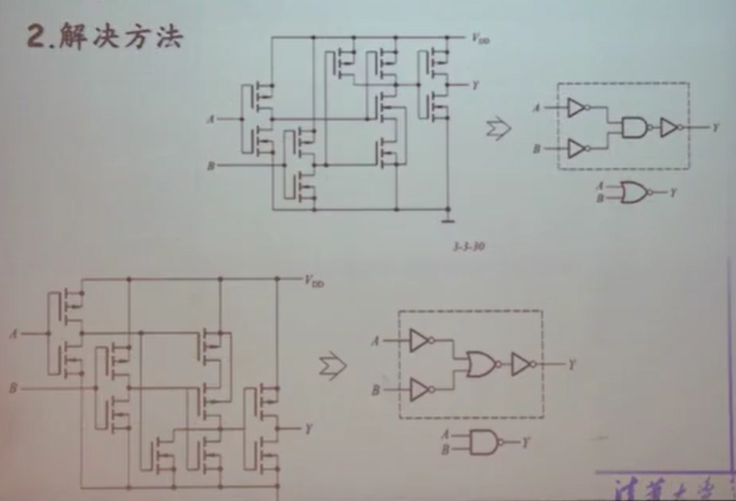

对于上述问题,我们有如下解决思路:

对于每一个输入输出都经过反相器,那么此时就将其输出电压质量的差异消除在反相器的噪声容限内。而此时设计与非门,实际上时采用或非门的结构,如下:

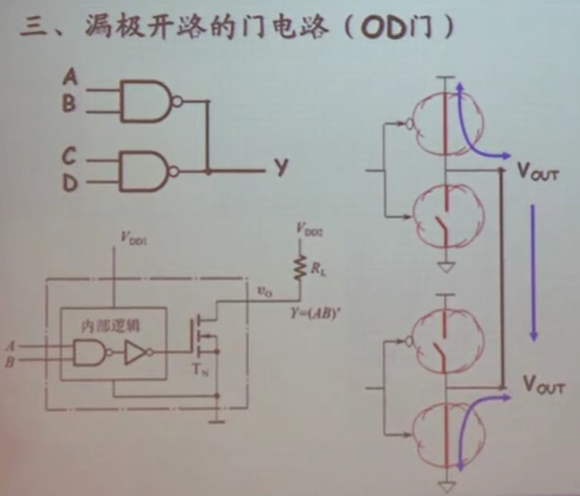

漏极开路的门电路(OD门)

OD门介绍

这种电路设计的思想来源于“线与”。在CMOS的电路设计中,线与操作时绝对不允许的,于是人们设计了OD门电路来解决这一问题,对于OD门电路而言,其前级按照正常的CMOS门电路进行设计。在最后一级时采用漏极开路。但是需要记住的,此时由于漏极开路,不能完成正常的上拉工作,于是需要外接电源和电阻的存在使得其能够正常输出高电平。

那么此时对于多个漏极开路的结构:

- 可以输出并联使用,实现“线与”或者用作电平转换、驱动器。

- 使用时外界$R_{L},V_{DD}^{‘}$,其中$V_{DD}^{‘}$可以不等于$V_{DD}$,于是也就是说此时可以调整输出电压值。

$R_{L}$的计算方法

上述要求主要有两个:

- $V_{DD} - (nI_{OH}+mI_{IH}) \geq V_{OH}$,也就是:$R_{L} \leq (V_{DD} - V_{OH})/(nI_{OH} + mI_{IH}) = R_{Lmax}$

- 同理,当输出为低电平时,负载电阻要起到保护作用,也就是:$(V_{DD} - V_{OL})/R_{L} + m^{‘}|I_{IL}| \leq I_{OLmax}$,于是此时我们能够计算出一个下限:$R_{L} \geq (V_{DD}-V_{OL})/(I_{OLmax}-m’|I_{IL}|)=R_{Lmin}$

综合上述两方面,于是得到$R_{Lmin} \leq R_{L} \leq R_{Lmin}$.

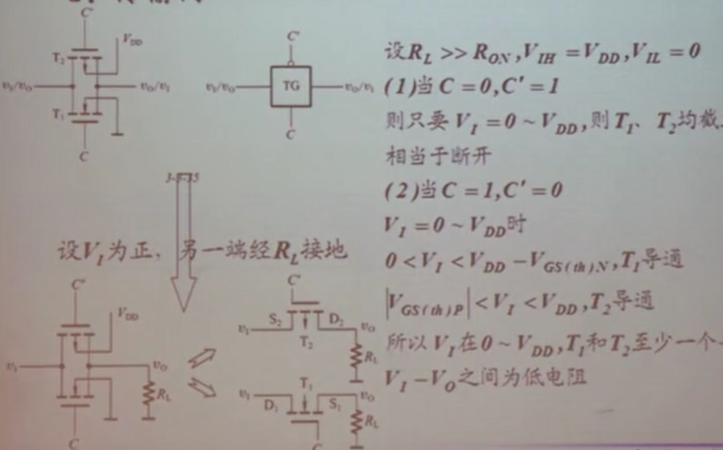

CMOS传输门以及双向模拟开关

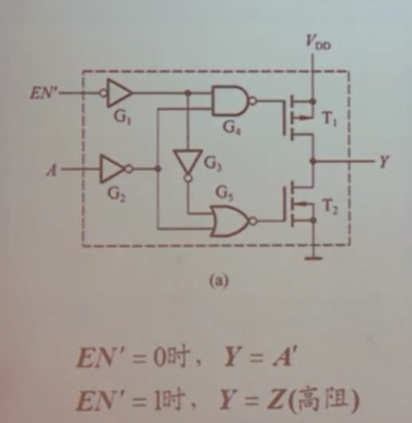

三态门

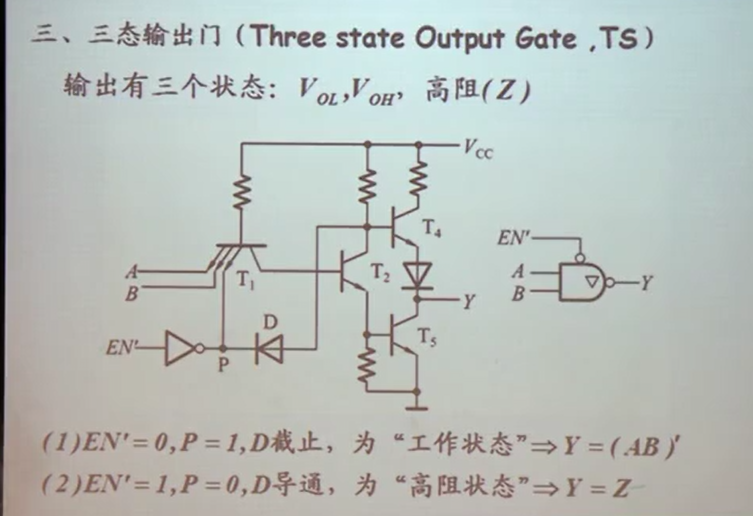

三态门的用途可以用于总线,在总线中只有一个使能,其他全为高阻态。

TTL门电路

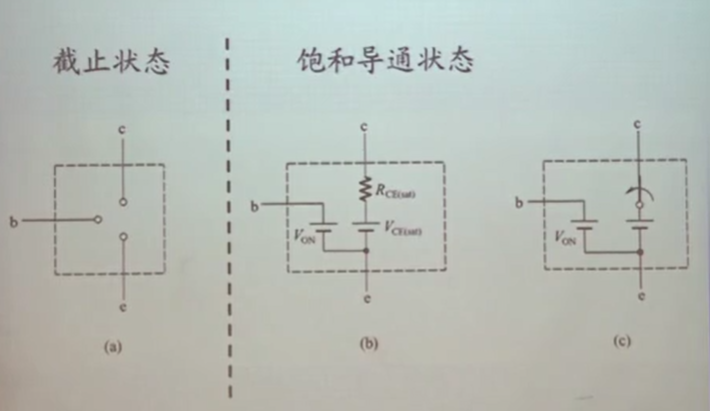

双极型三极管的特性

双极型三极管的基本开关电路

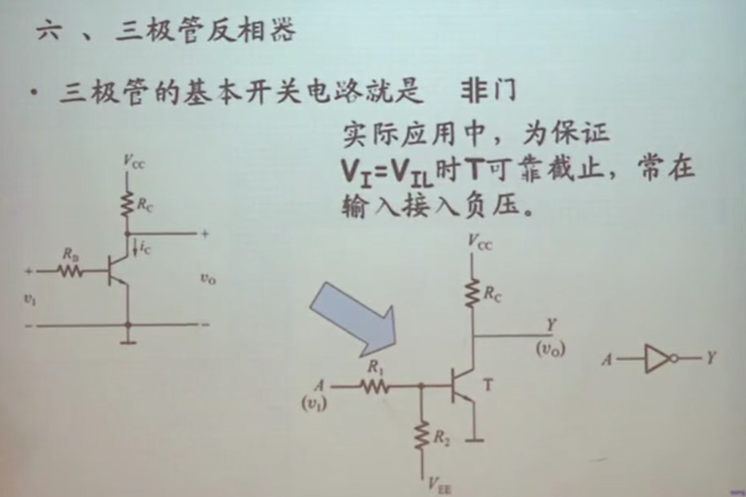

三极管反相器

三极管作为反相器并不理想,因为其低电平不存在一个大的可变化范围,只能低于0.7。于是工程师考虑接入一个负压。但是这种设计在实际工程中不推荐。

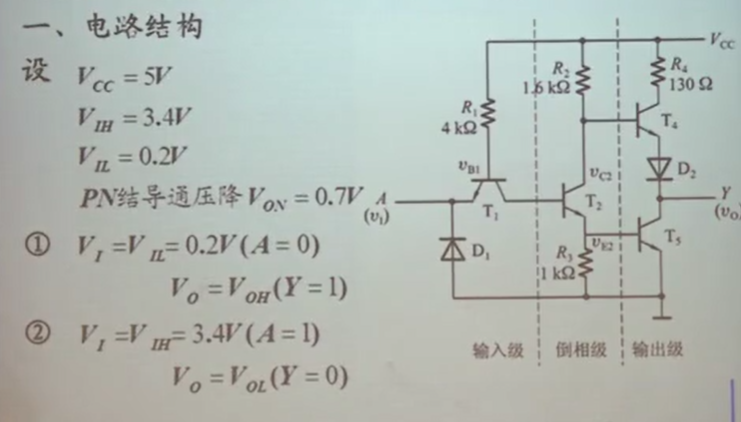

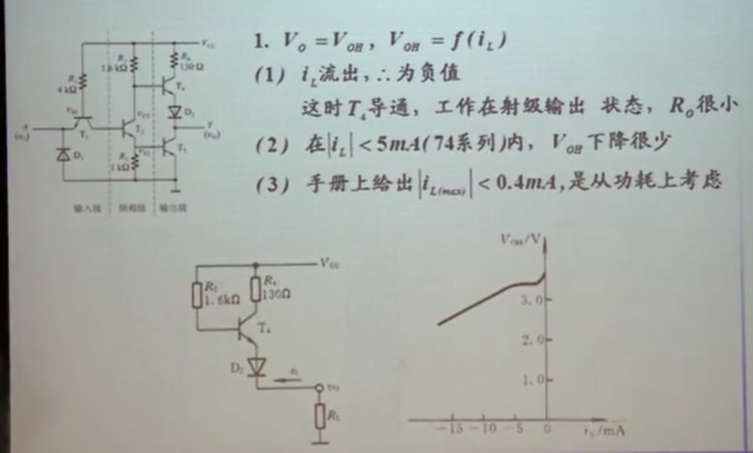

TTL反相器的电路结构

需要说明的几个问题:

- $T_{2}$的输出$V_{C2}$和$V_{e2}$的变化方向相反,因此中间级也成为倒相级。

- 输出级在稳态下,$T_{4},T_{5}$总有一个导通,一个截止,既能降低功耗,又提高了带负载能力,称为推拉式。

- $D_{1}$已知负向干扰,$D_{2}$保证$T_{5}$导通时,$T_{4}$可靠截止。

输入噪声容限

TTL反相器

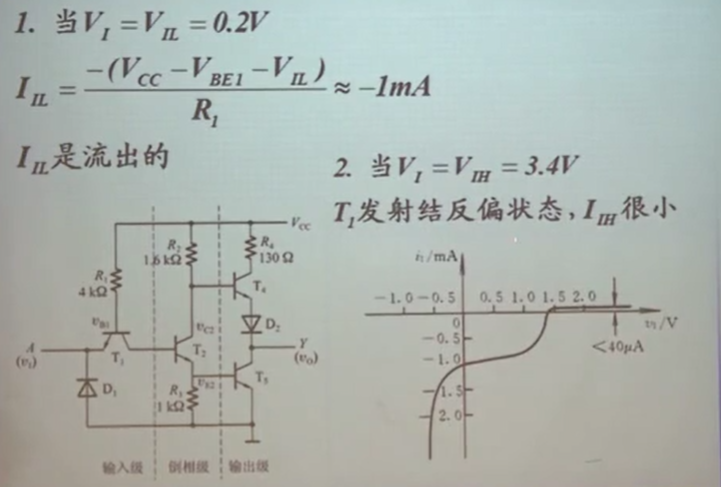

TTL反相器输入特性

TTL反相器的输出特性

输入端负载特性

扇出系数

扇出系数指的是某个数字器件能够驱动其同类型器件的个数。

传输延迟时间

传输延迟时间可以分为两个阶段。

- $t_{PD}$:在输入信号发生变化的时候,输入信号必然是从一个有效信号到另外一个有效信号,而在有效到有效的过程中,一定会经过无效,于是传输延迟时间本质上也就是一个有效状态到另外一个有效状态所花费的时间。

- $t_{CD}$:无效信号也会在电路中传播,此参数描述的是输出从有效区转入无效区所用时间。

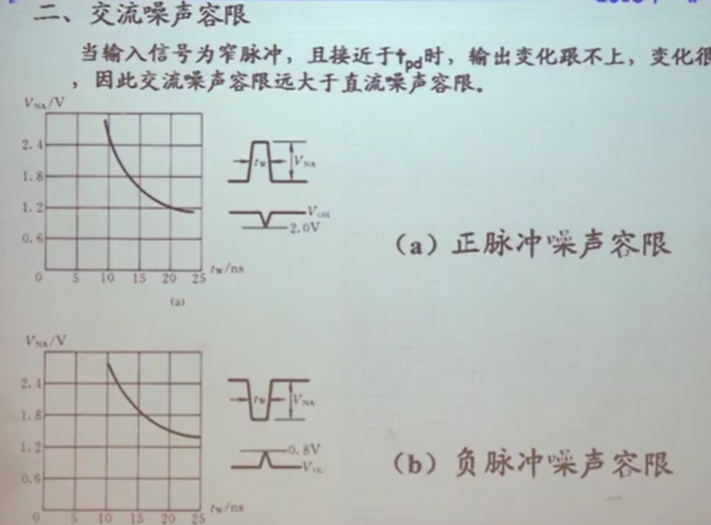

交流噪声容限

动态尖峰电流

其他类型的TTL门

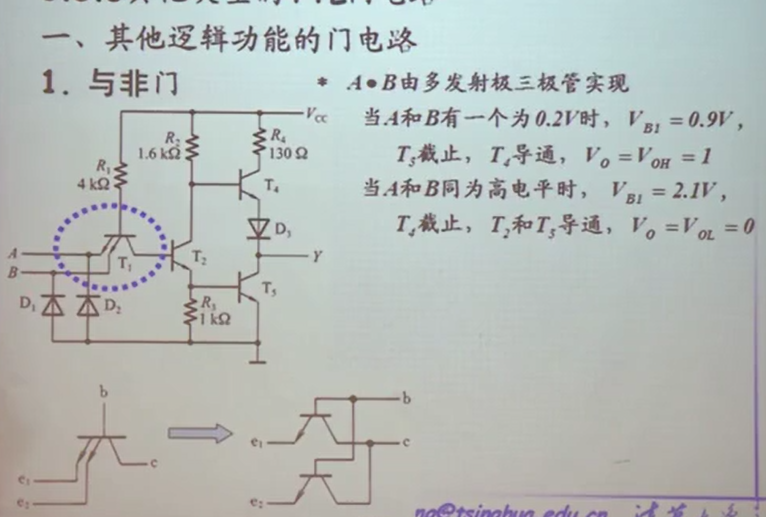

与非门

或非门

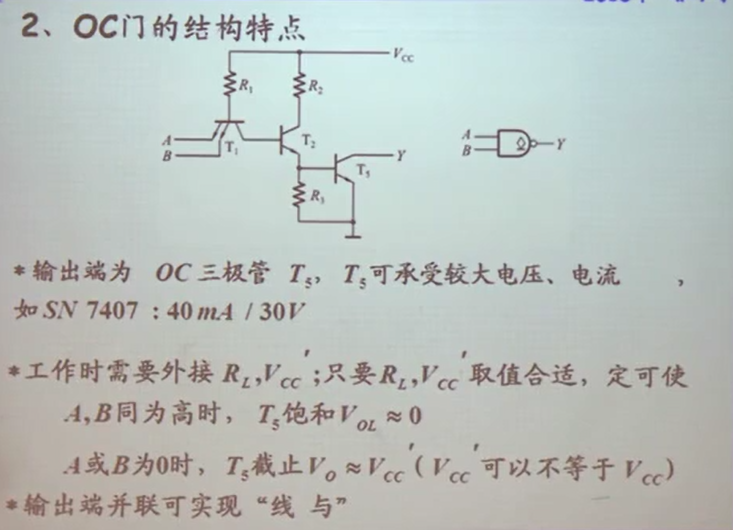

OC门

OC门对应与CMOS中的OD门,其特性如下:

此时可以利用OC门实现“线与”运算,当$Y_{1},Y_{2}$有一个低即为低,只有两者同为高,Y才为高,所以:$Y=Y_{1}Y_{2}=(AB)’(CD)’=(AB+CD)’$.

三态输出门